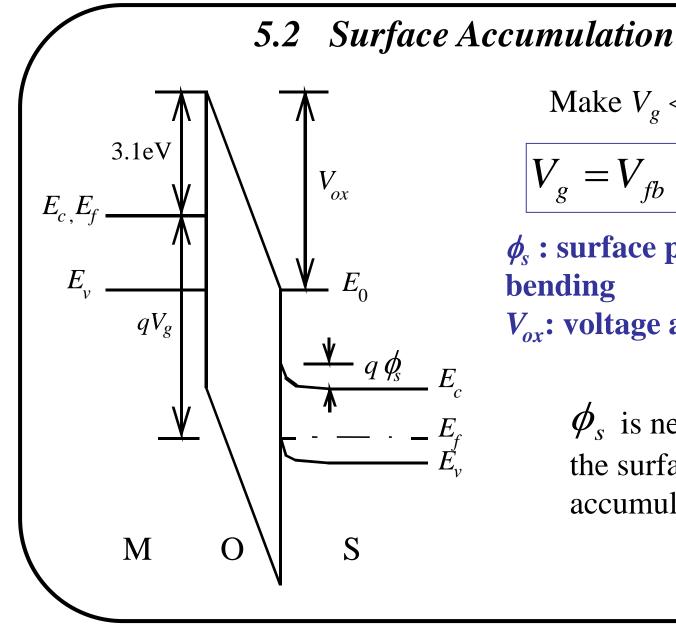

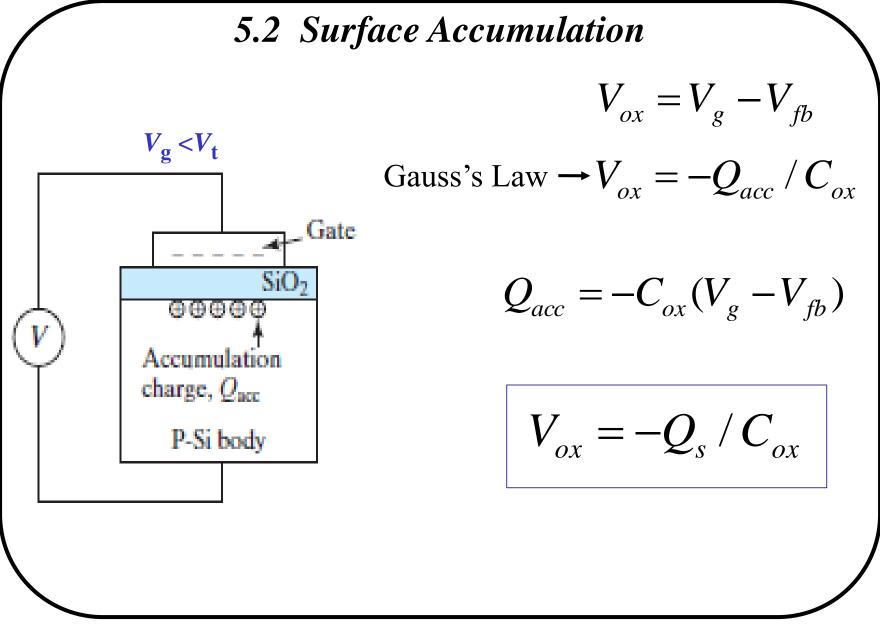

Make

$$V_g < V_{fb}$$

$$V_g = V_{fb} + \phi_s + V_{ox}$$

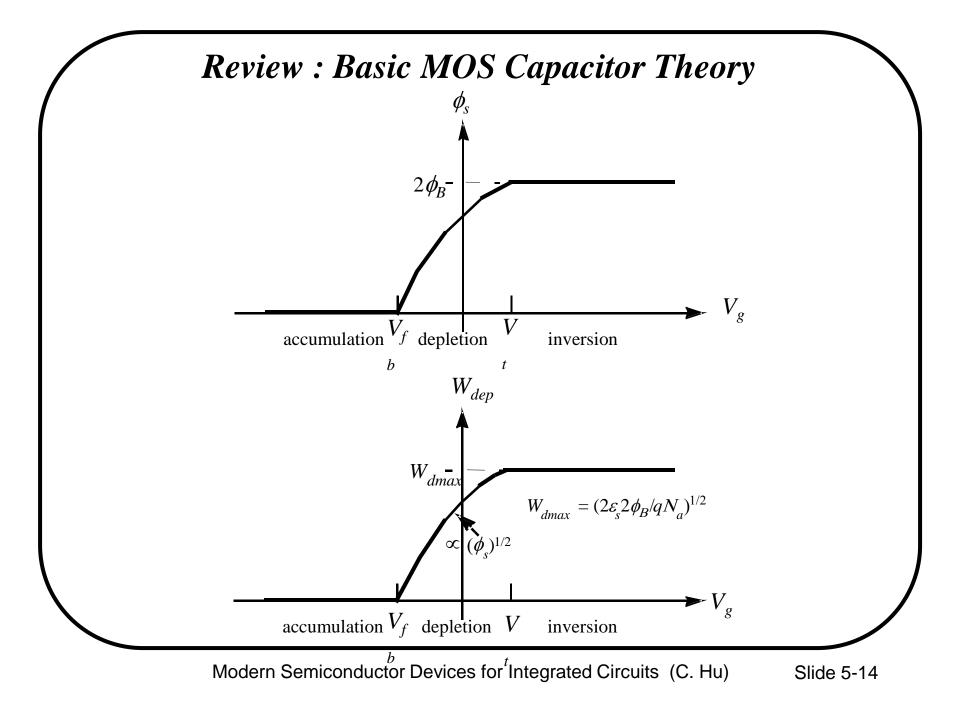

$\phi_{s}$ : surface potential, band bending  $V_{or}$ : voltage across the oxide

> $\phi_s$  is negligible when the surface is in accumulation.

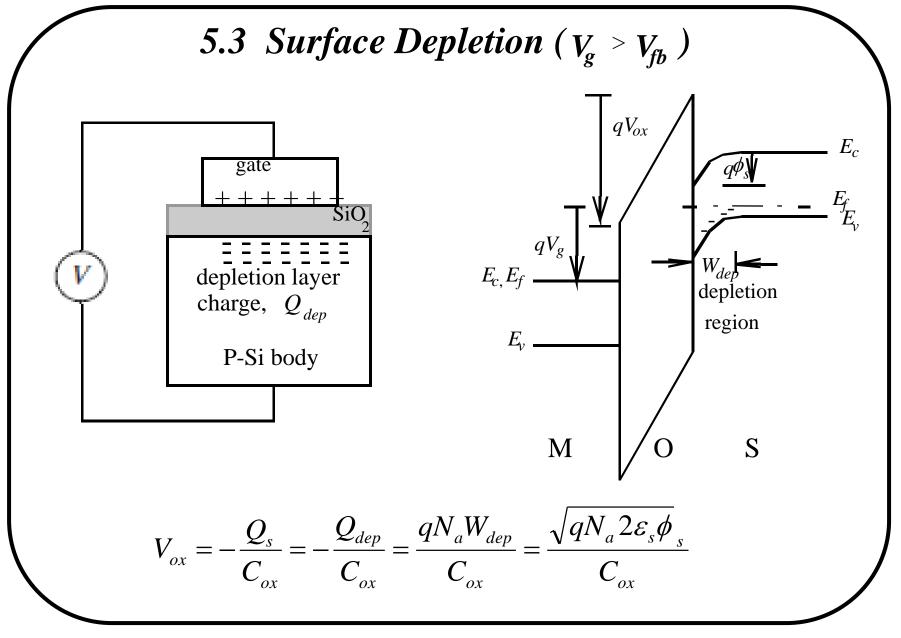

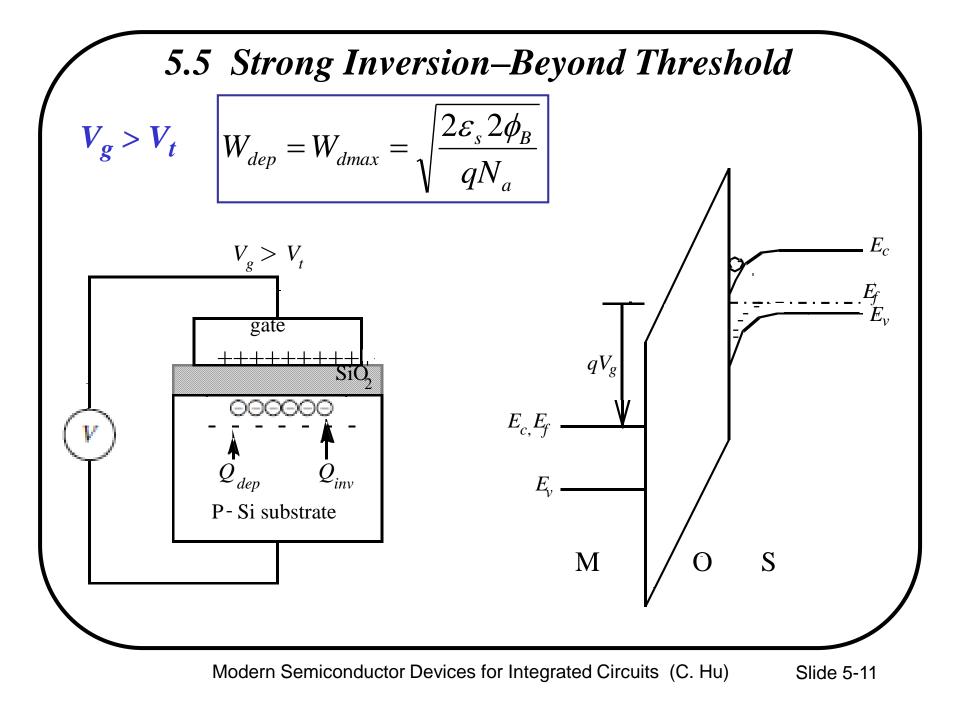

#### 5.3 Surface Depletion

$V_g = V_{fb} + \phi_s + V_{ox} = V_{fb} + \phi_s + \frac{\sqrt{qN_a 2\varepsilon_s \phi_s}}{C}$

This equation can be solved to yield  $\phi_s$ .

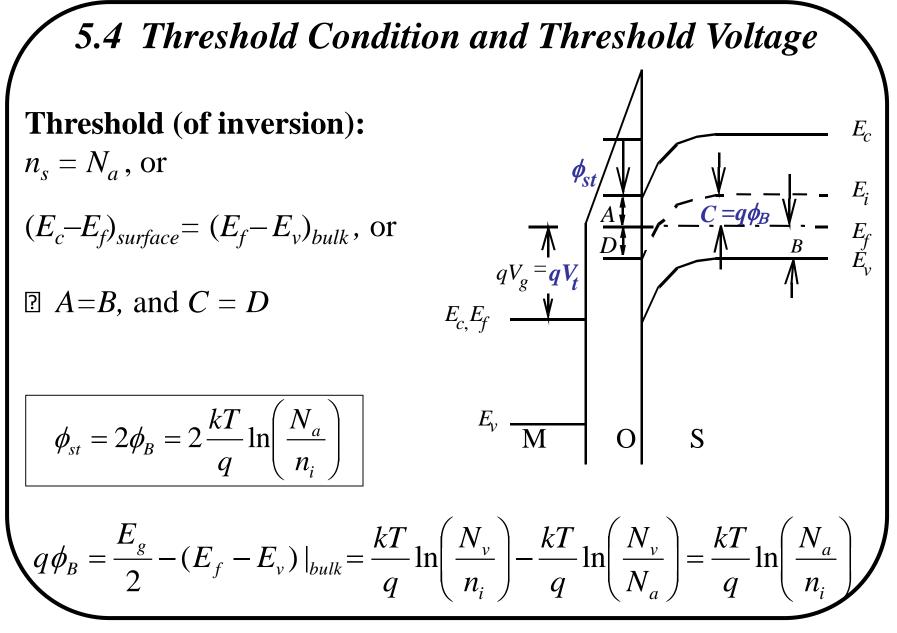

#### Threshold Voltage

$$V_g = V_{fb} + \varphi_s + V_{ox}$$

#### At threshold,

$$\varphi_{st} = 2\phi_B = 2\frac{kT}{q}\ln\left(\frac{N_a}{n_i}\right)$$

$$V_{ox} = \frac{\sqrt{qN_a 2\varepsilon_s 2\phi_B}}{C_{ox}}$$

$$V_t = V_g \text{ at threshold} = V_{fb} + 2\phi_B + \frac{\sqrt{qN_a 2\varepsilon_s 2\phi_B}}{C_{ox}}$$

Threshold Voltage

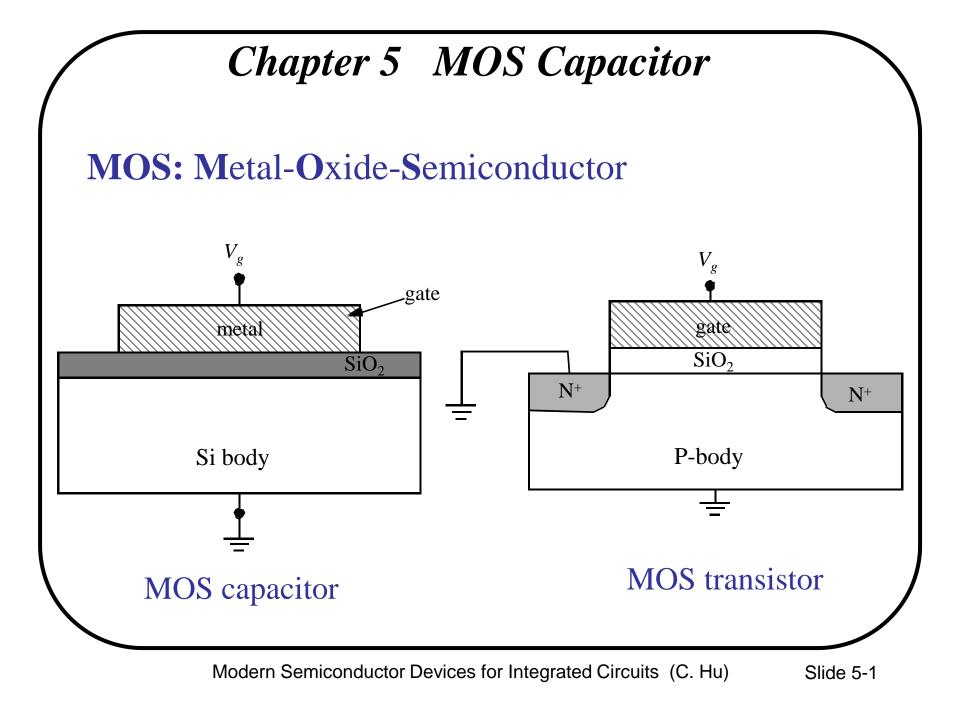

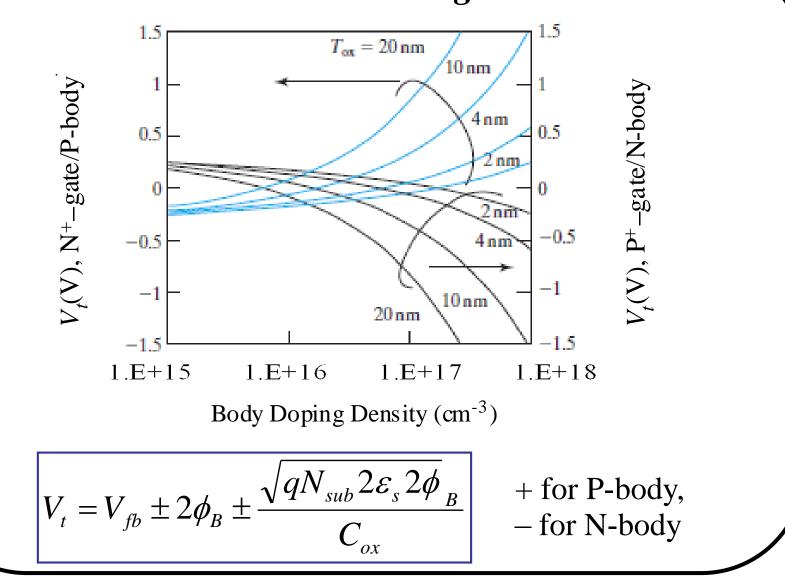

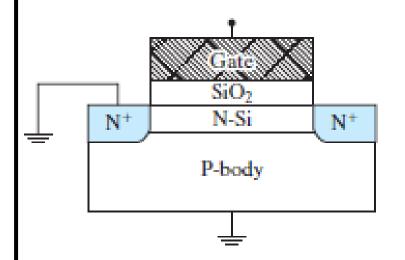

# 5.5.1 Choice of V<sub>t</sub> and Gate Doping Type

$V_t$  is generally set at a small positive value so that, at  $V_g =$ 0, the transistor does not have an inversion layer and current does not flow between the two N<sup>+</sup> regions

• P-body is normally paired with N<sup>+</sup>-gate to achieve a small positive threshold voltage.

• N-body is normally paired with P<sup>+</sup>-gate to achieve a small negative threshold voltage.

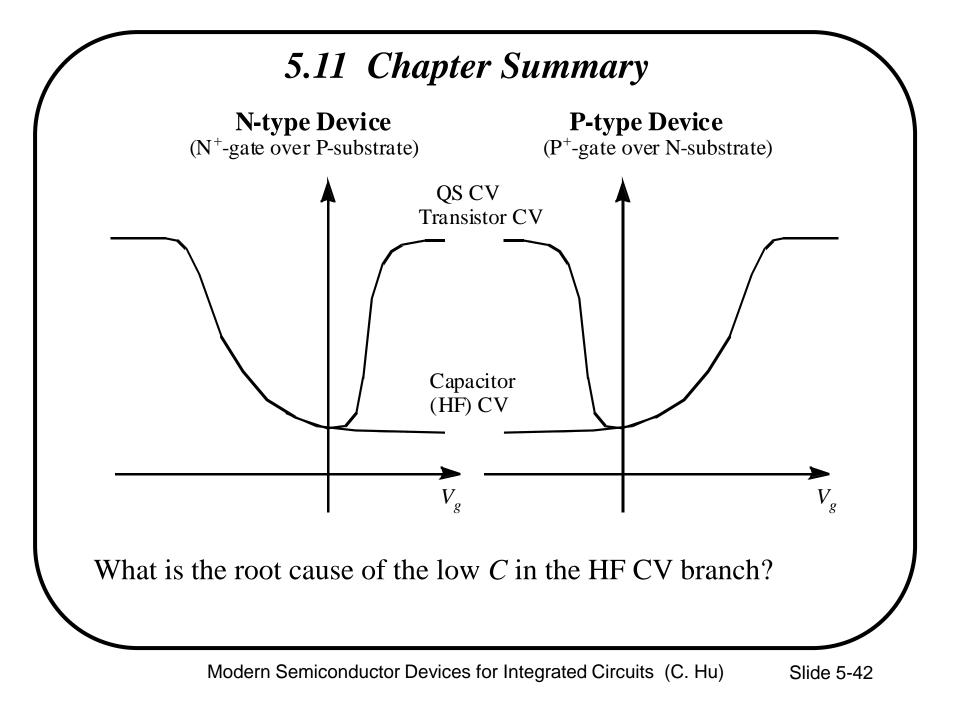

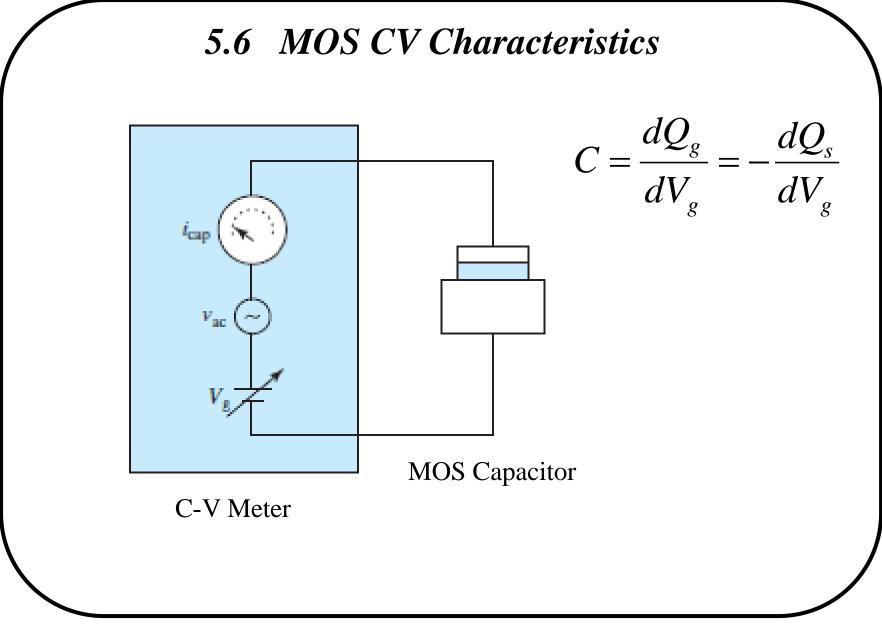

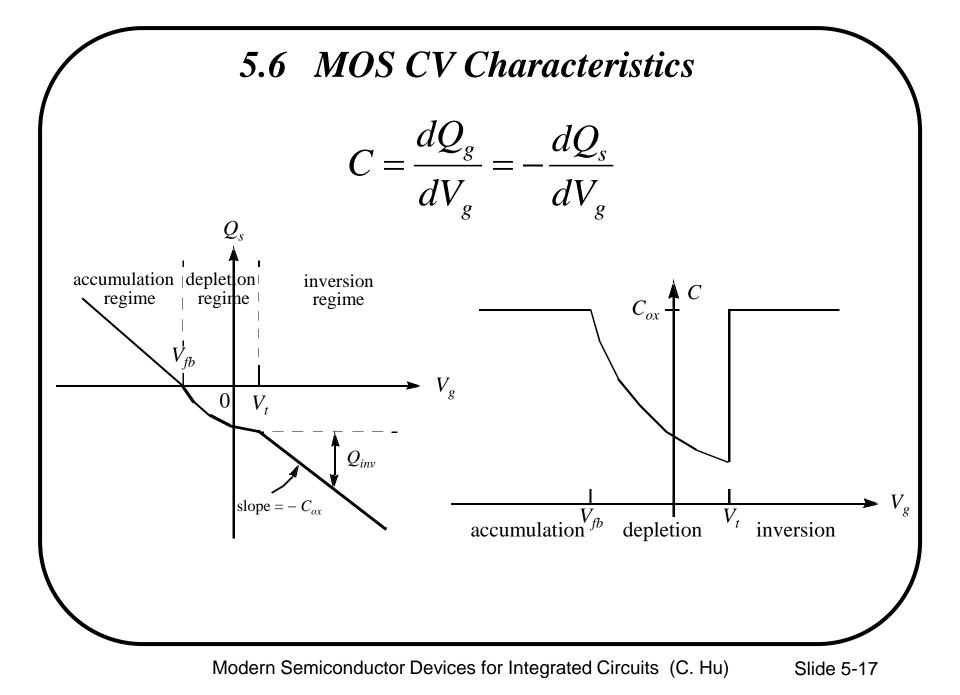

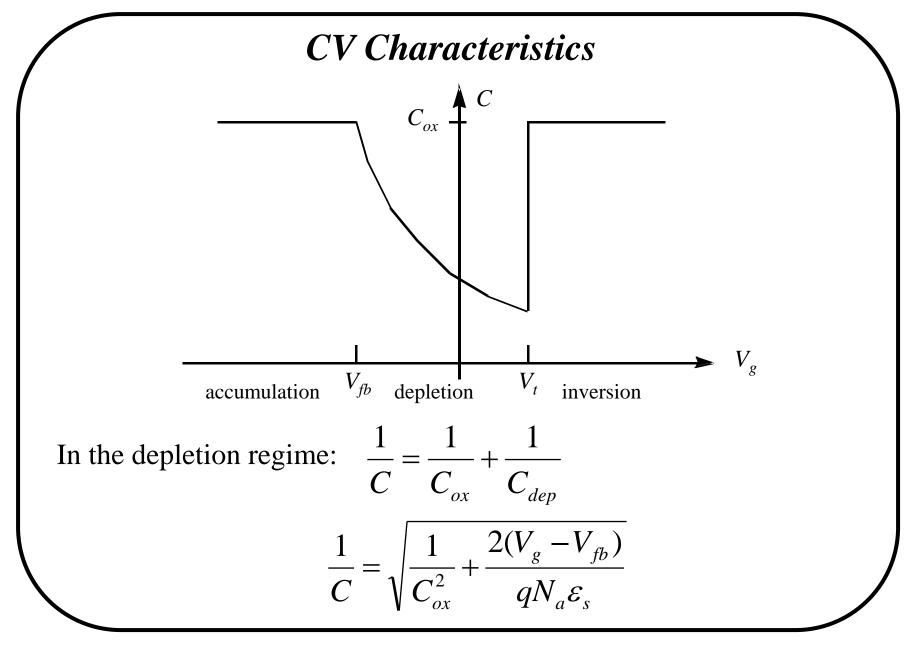

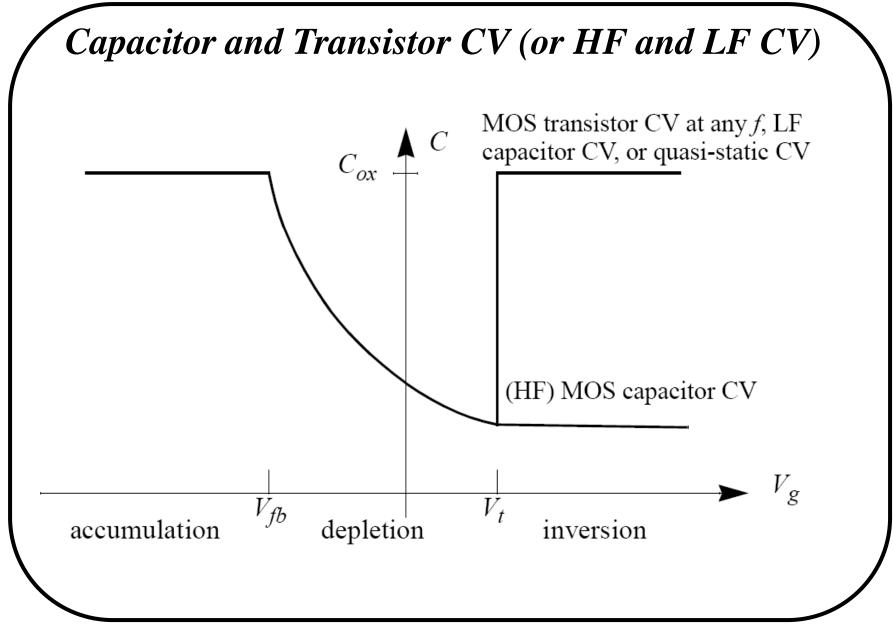

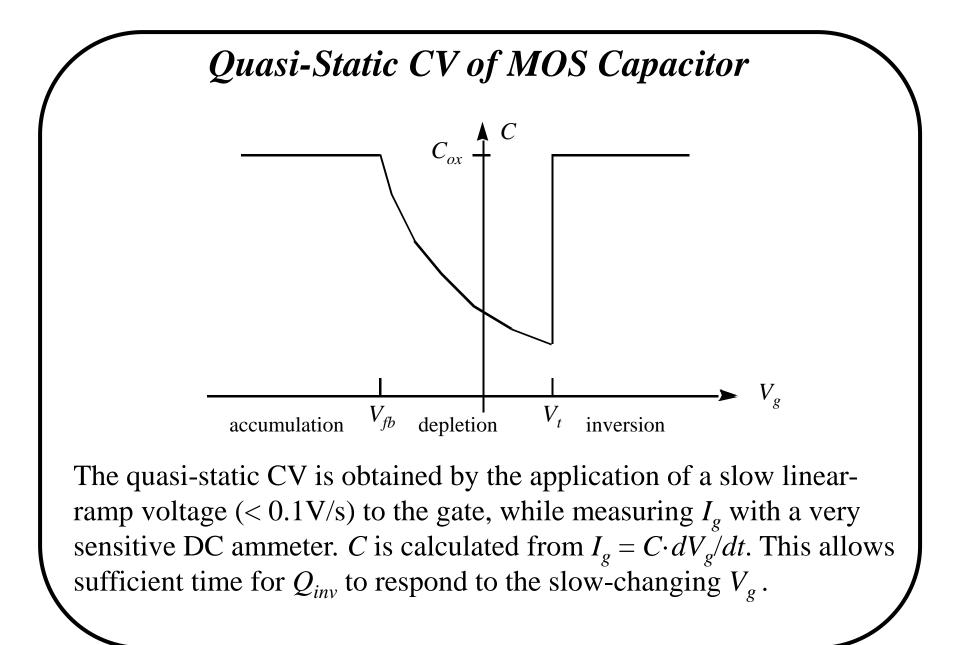

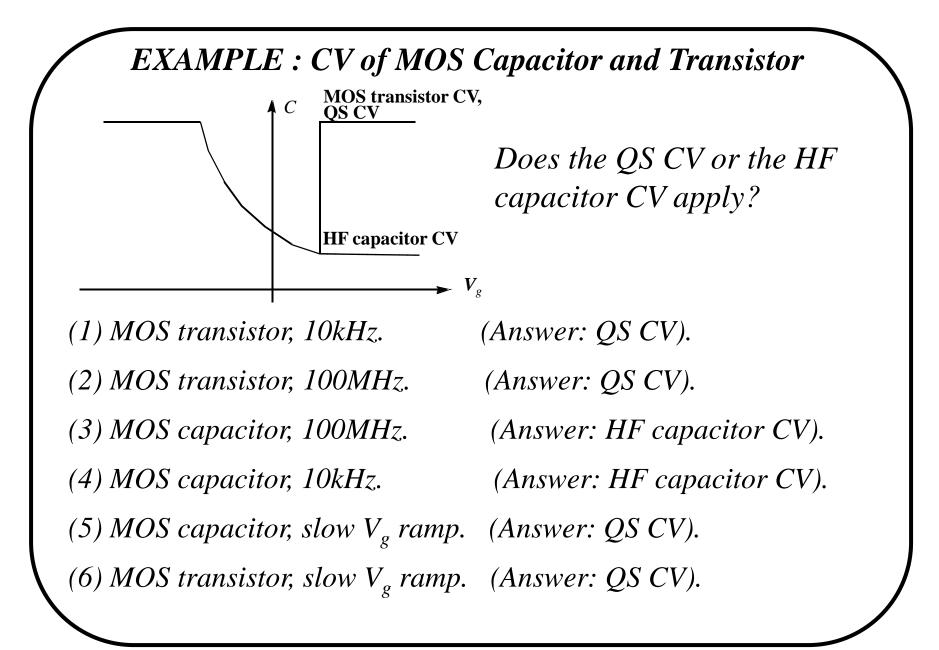

Supply of Inversion Charge May be Limited gate gate  $C_{ox}$  $C_{ox}$ Cdep Accumulation **Depletion P-substrate P-substrate** gate gate  $C_{ox}$  $C_{ox}$ <u>୦୦୦୦୦୦୦୦</u> -**→**10 00000000 Inversion dmax DC and AC  $W_{dmax}$ **Inversion**<sup>*W*<sub>dmax</sub></sup> **P-substrate** P-substrate In each case, C = ?

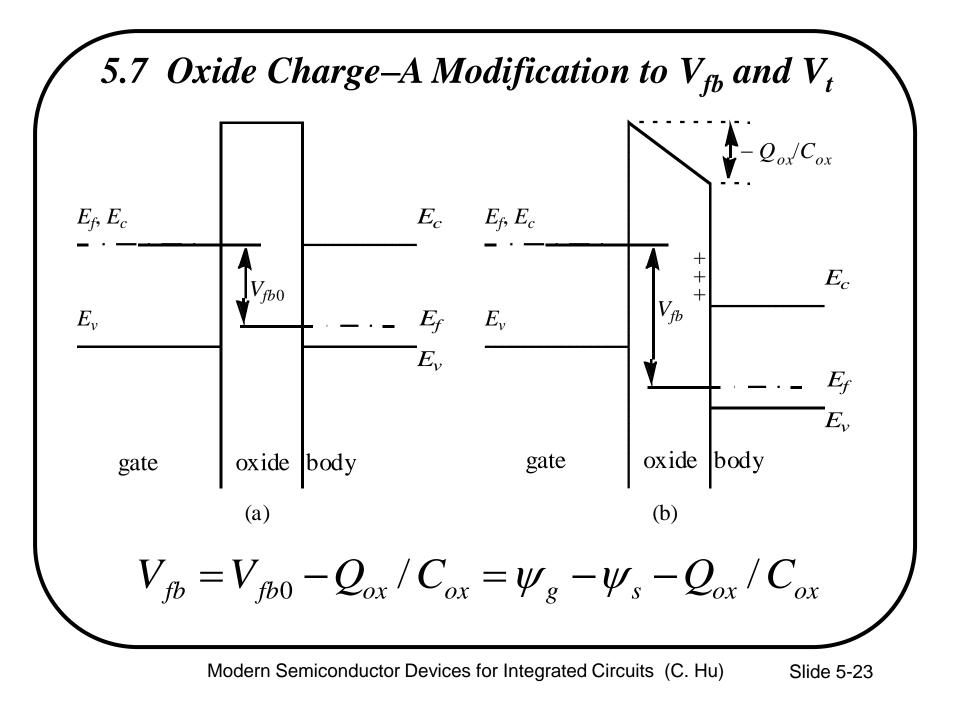

# 5.7 Oxide Charge–A Modification to $V_{fb}$ and $V_t$

### Types of oxide charge:

- Fixed oxide charge, Si<sup>+</sup>

- Mobile oxide charge, due to Na<sup>+</sup>contamination

- Interface traps, neutral or charged depending on Vg.

- Voltage/temperature stress induced charge and traps--a reliability issue

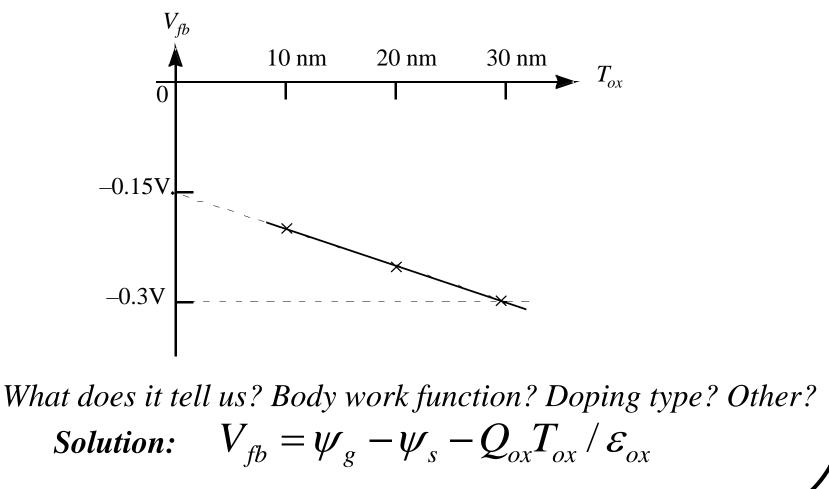

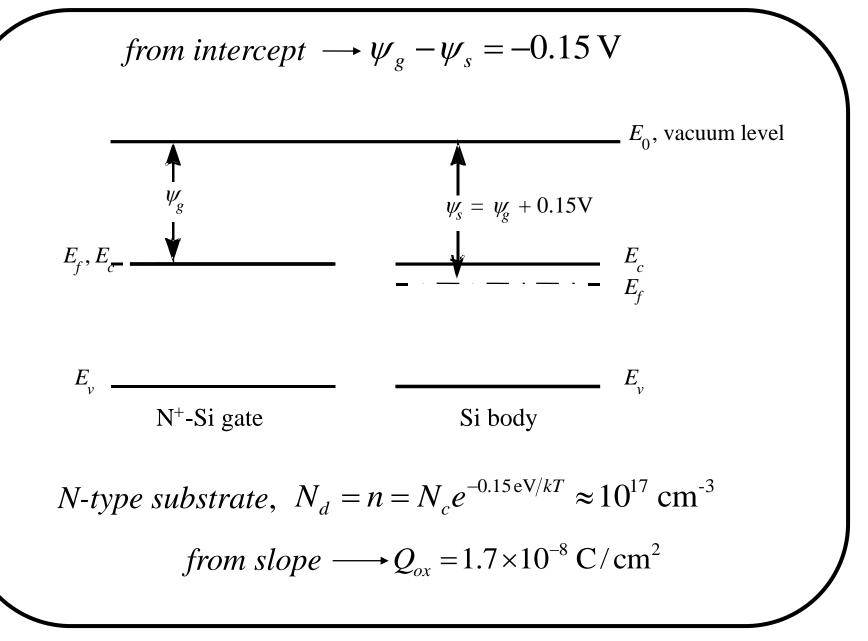

**EXAMPLE:** Interpret this measured  $V_{fb}$  dependence on oxide thickness. The gate electrode is  $N^+$  poly-silicon.

Modern Semiconductor Devices for Integrated Circuits (C. Hu) Slide 5-26

Modern Semiconductor Devices for Integrated Circuits (C. Hu) Slide 5-27

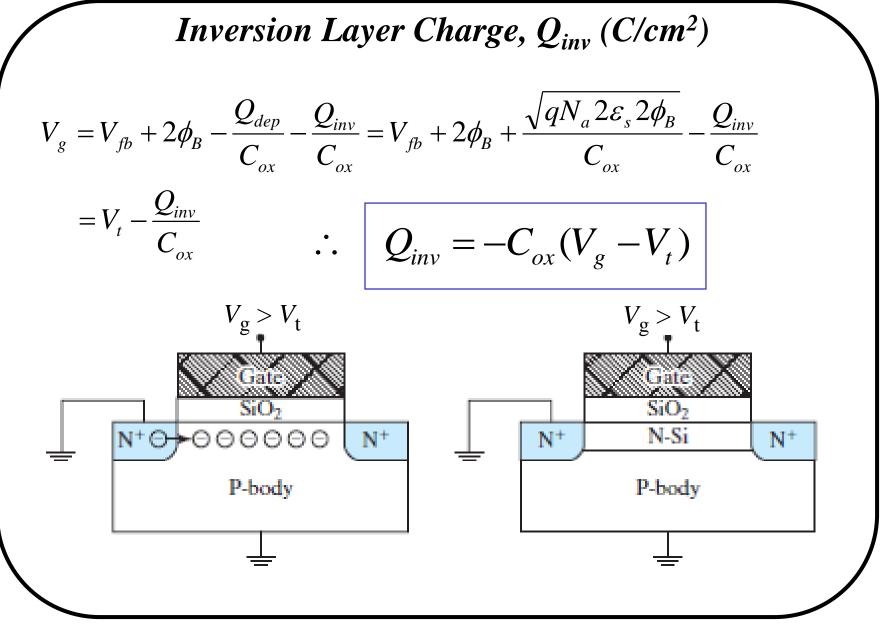

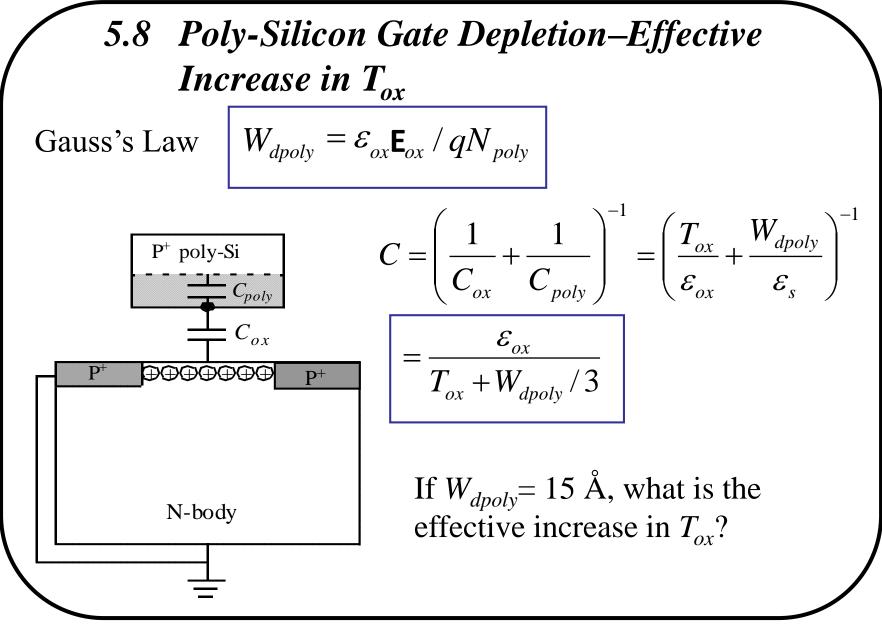

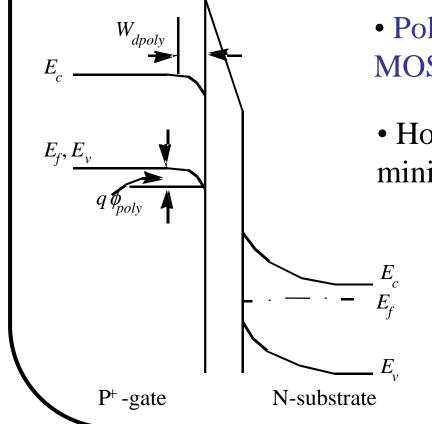

#### Effect of Poly-Gate Depletion on $Q_{inv}$

$$Q_{inv} = C_{ox}(V_g - \phi_{poly} - V_t)$$

- Poly-gate depletion degrades MOSFET current and circuit speed.

- How can poly-depletion be minimized?

#### **EXAMPLE : Poly-Silicon Gate Depletion**

$V_{ox}$ , the voltage across a 2 nm thin oxide, is -1 V. The P<sup>+</sup> polygate doping is  $N_{poly} = 8 \times 10^{19}$  cm<sup>-3</sup> and substrate  $N_d$  is  $10^{17}$ cm<sup>-3</sup>. Find (a)  $W_{dpoly}$ , (b)  $\phi_{poly}$ , and (c)  $V_g$ .

Solution:

(a)

$$W_{dpoly} = \varepsilon_{ox} \mathbf{E}_{ox} / qN_{poly} = \varepsilon_{ox} V_{ox} / T_{ox} qN_{poly}$$

$$= \frac{3.9 \times 8.85 \times 10^{-14} (\text{F/cm}) \times 1 \text{V}}{2 \times 10^{-7} \text{cm} \times 1.6 \times 10^{-19} \text{C} \times 8 \times 10^{19} \text{cm}^{-3}}$$

$$= 1.3 \text{ nm}$$

# **EXAMPLE : Poly-Silicon Gate Depletion**

(b)

$$W_{dpoly} = \sqrt{\frac{2\varepsilon_s \phi_{poly}}{qN_{poly}}}$$

$$\phi_{dpoly} = q N_{poly} W_{dpoly}^2 / 2\varepsilon_s = 0.11 \,\mathrm{V}$$

(c)

$$V_g = V_{fb} + \phi_{st} + V_{ox} + \phi_{poly}$$

$V_{fb} = \frac{E_g}{q} - \frac{kT}{q} \ln\left(\frac{N_c}{N_d}\right) = 1.1 \text{ V} - 0.15 \text{ V} = 0.95 \text{ V}$

$V_g = 0.95 \text{ V} - 0.85 \text{ V} - 1 \text{ V} - 0.11 \text{ V} = -1.01 \text{ V}$

Is the loss of 0.11 V from the 1.01 V significant?

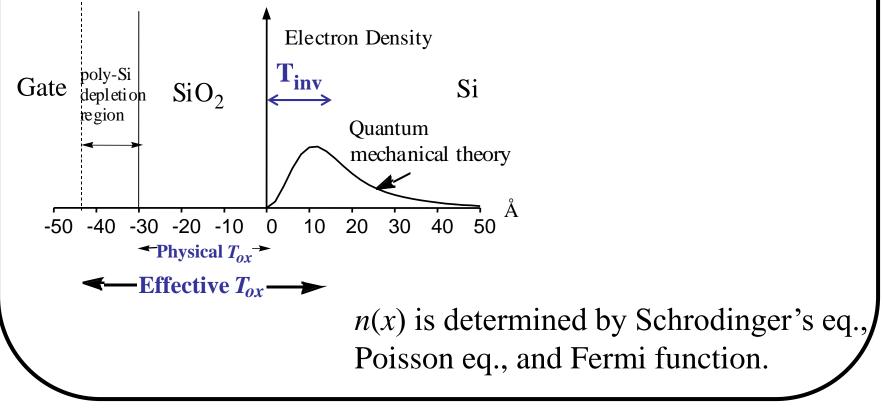

# **5.9 Inversion and Accumulation Charge-Layer** Thickness–Quantum Mechanical Effect

Average inversion-layer location below the Si/SiO<sub>2</sub> interface is called the *inversion-layer thickness*,  $T_{inv}$ .

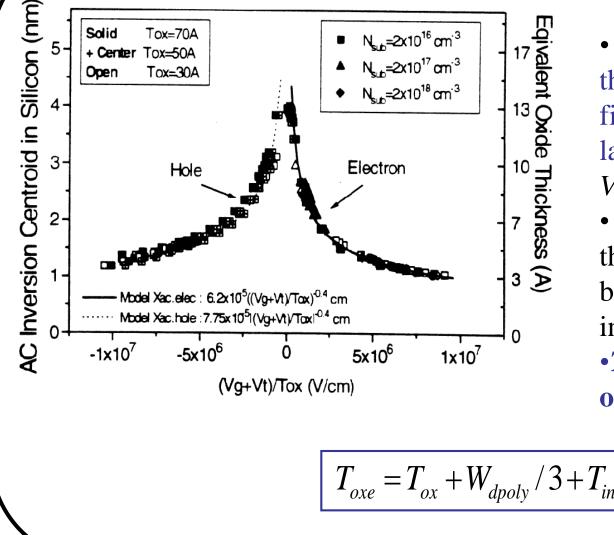

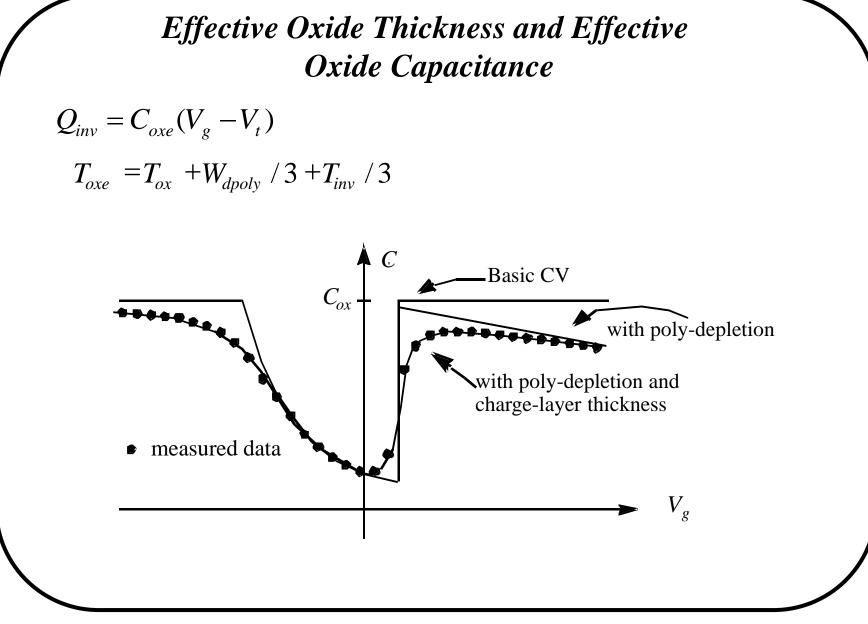

#### Electrical Oxide Thickness, T<sub>oxe</sub>

•  $T_{inv}$  is a function of the average electric field in the inversion layer, which is  $(V_{q} +$  $V_t$ )/6 $T_{ox}$  (Sec. 6.3.1). •  $T_{inv}$  of holes is larger than that of electrons because of difference in effective mass. • $T_{oxe}$  is the electrical

oxide thickness.

$$T_{oxe} = T_{ox} + W_{dpoly} / 3 + T_{inv} / 3 \quad \text{at } V_g = V_{dd}$$

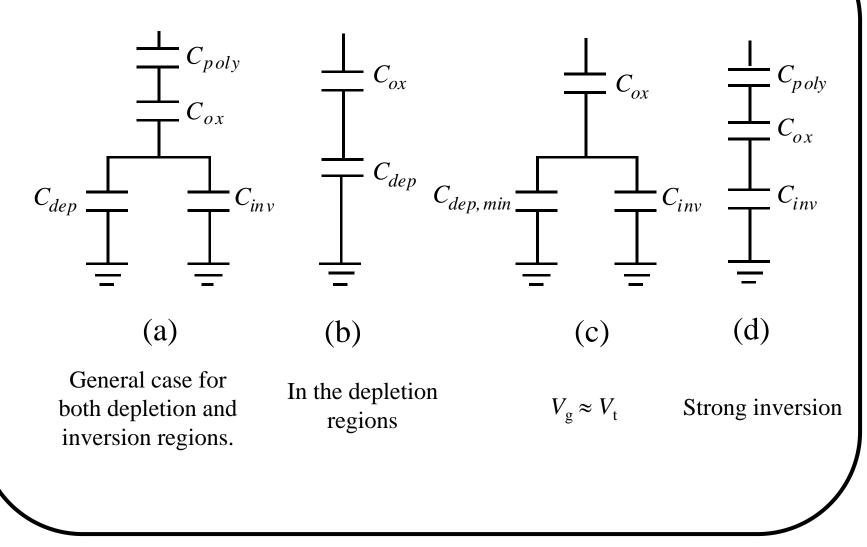

Equivalent circuit in the depletion and the inversion regimes

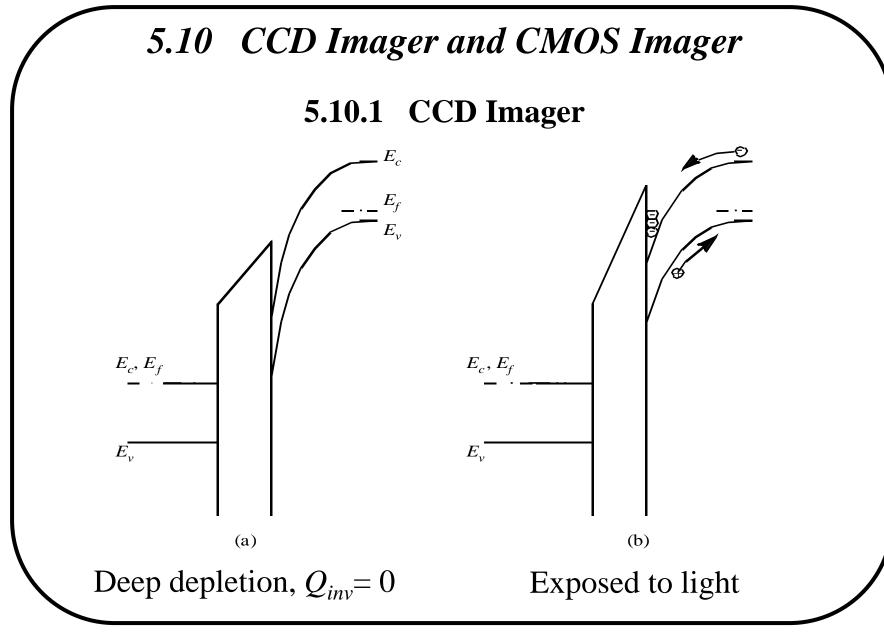

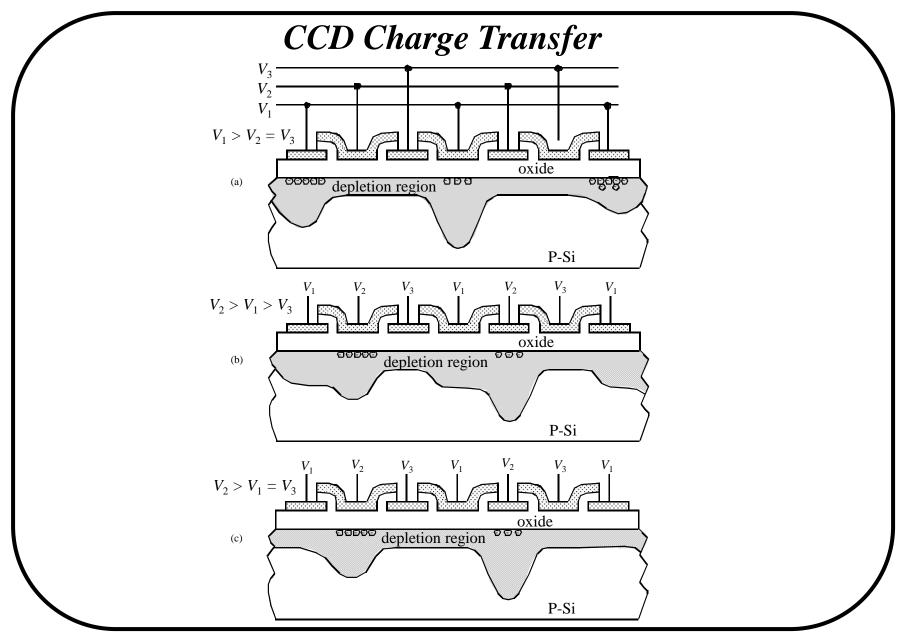

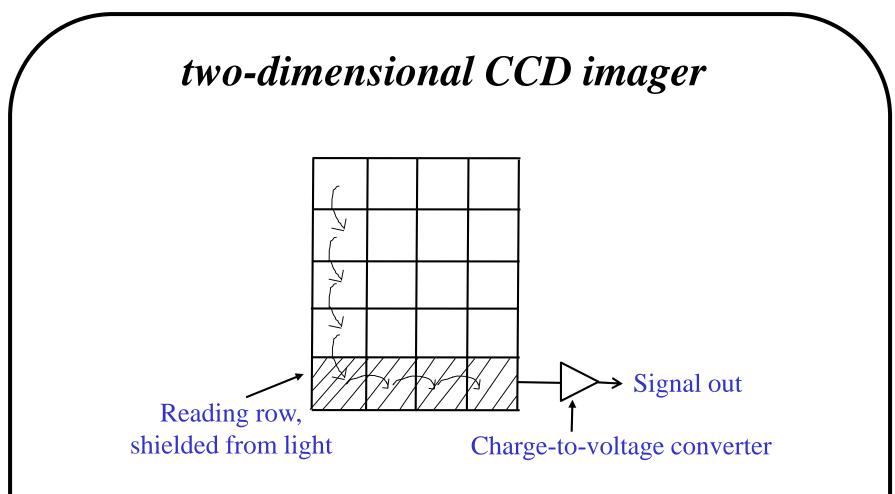

The reading row is shielded from the light by a metal film. The 2-D charge packets are read row by row.

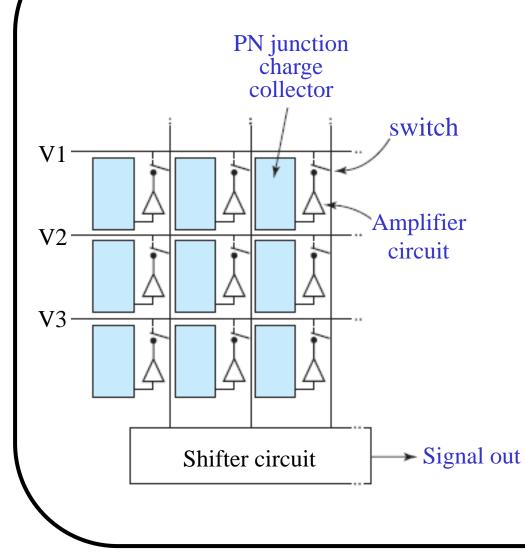

# 5.10.2 CMOS Imager

CMOS imagers can be integrated with signal processing and control circuitries to further reduce system costs. However, The size constrain of the sensing circuits forces the CMOS imager to use very simple circuits

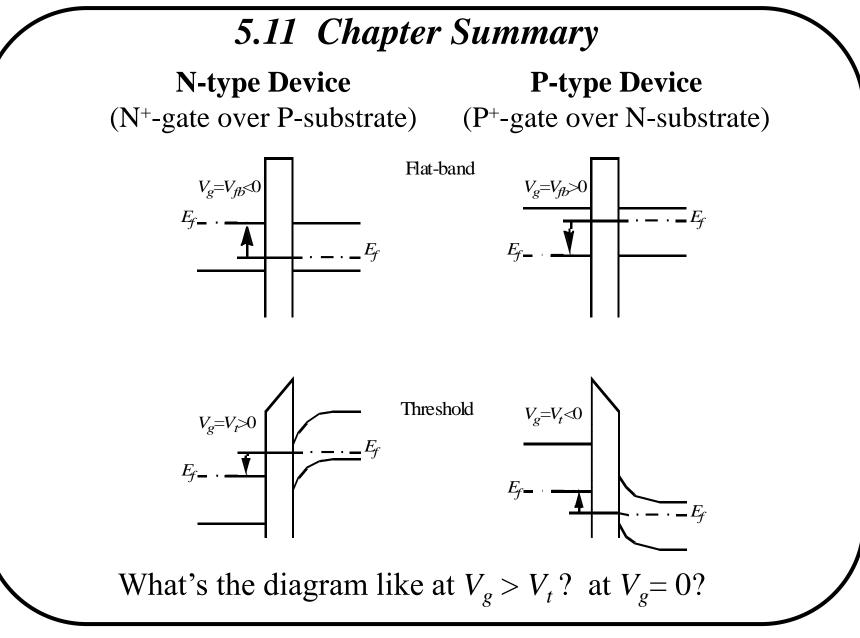

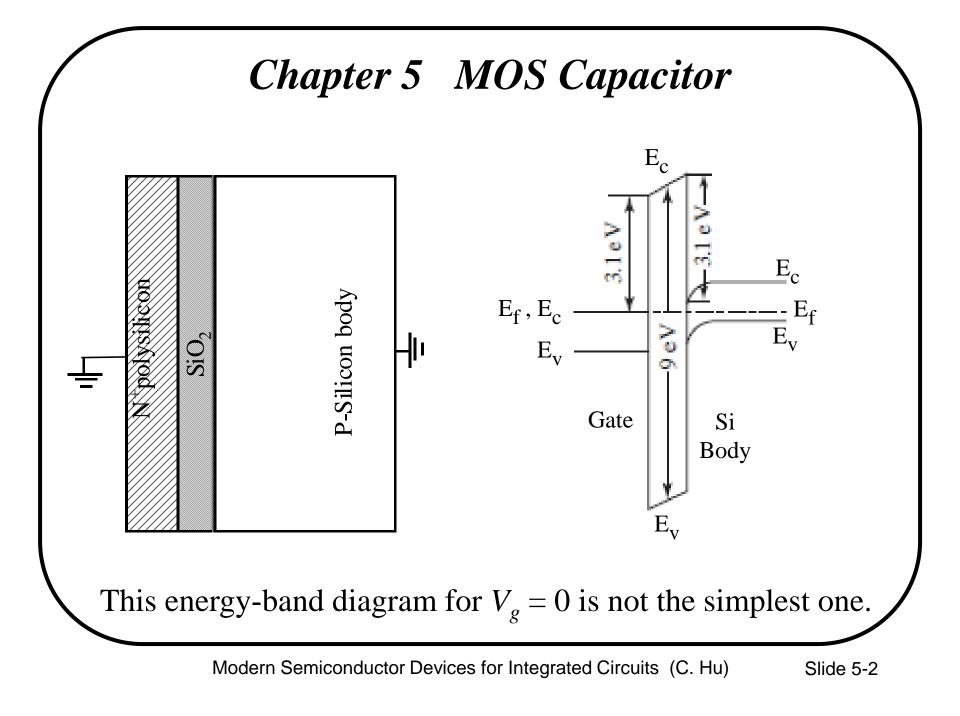

#### 5.11 Chapter Summary

N-type device: N<sup>+</sup>-polysilicon gate over P-body P-type device: P<sup>+</sup>-polysilicon gate over N-body

$$V_{fb} = \psi_g - \psi_s + (-Q_{ox} / C_{ox})$$

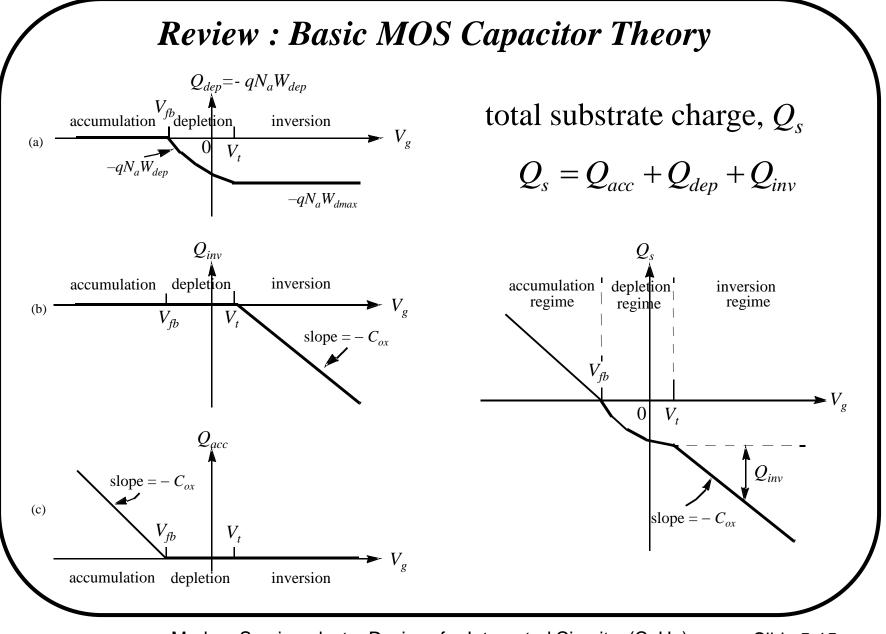

$$V_g = V_{fb} + \phi_s + V_{ox} + \phi_{poly}$$

$$= V_{fb} + \phi_s - Q_s / C_{ox} + \phi_{poly}$$

#### 5.11 Chapter Summary

$$\phi_{st} = \pm 2\phi_B$$

or  $\pm (\phi_B + 0.45 \text{ V})$

$$\phi_B = \frac{kT}{q} \ln \frac{N_{sub}}{n_i}$$

$$V_{t} = V_{fb} + \phi_{st} \pm \frac{\sqrt{qN_{sub}}2\varepsilon_{s} |\phi_{st}|}{C_{ox}}$$

+ : N-type device, -: P-type device